システムの高度化は加速度的に進み、短期間で安定したシステムを開発することはますます困難になってきています。当社PARTNER-Jetファミリは、先進的なデバッグ技術をいち早く取込み、お客様のシステム開発を支援してきました。

これからも、お客様システムの短期開発&高品質化に貢献する製品を提供していきます。

概要

PARTNER-Jet3は、PARTNER-Jetファミリの第3世代製品であり、高速化と使い勝手を両立した製品へさらに進化しています。

- 最新デバッグテクノロジを搭載

PARTNER-Jet3は、今後の開発技術トレンドを見据え、最先端のデバッグ技術を取り入れています。ソースコードデバッガとして、マルチコア対応をはじめ、LinuxなどOSアプリケーションのデバッグ対応、実行停止せずアプリケーション状態を監視するRAMモニタ機能などを取り入れています。また、従来利用されてきたC/C++言語によるアプリケーション開発に加え、最近注目されているRust言語でのデバッグにもいち早く対応しています。 - 広範なアプリケーション開発に対応

PARTNER-Jet3は、発売以来、民生分野、アミューズメント分野、産業分野のアプリケーション開発に加え、高度な安全/信頼性機能が要求される車載分野や医療分野などのアプリケーション開発にもご利用頂いています。また、マイコン搭載の制御系システムから、プロセッサ/SoCを搭載したデータ処理系システムまで幅広いアプリケーション開発で使用されています。 - 様々なCPUに対応

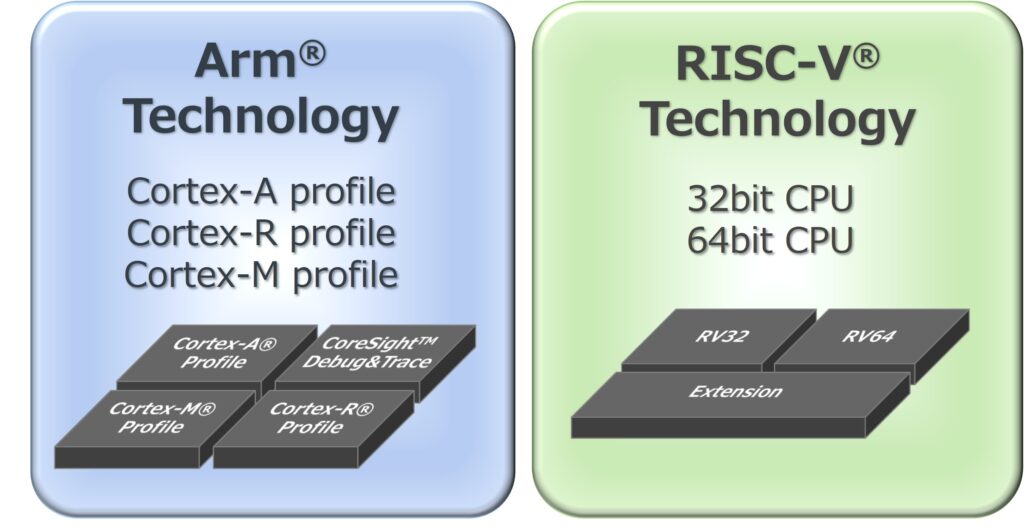

組込みシステム向けCPUとしてメジャーなArm®コア、RISC-Vコアに対応しています。1台のPARTNER-Jet3で、CPUコアや半導体ベンダに縛られることなく、様々なシステム開発でご利用頂けます。 - 充実したサポート体制とロングライフサポート

PARTNER-Jet3の主要部品には、長期供給に実績ある半導体部品を採用することで、製品ロングライフ化を実現しています。また、PARTNER-Jet3製品は、すべて国内での製品開発・サポート体制を構築しており、技術サポートやドキュメントなども日本語で対応致します。

製品構成

PARTNER-Jet3デバッグシステムは、JTAGエミュレータ、JTAGプローブと、WindowsPCで動作するPARTNERデバッガソフトウェアで動作します

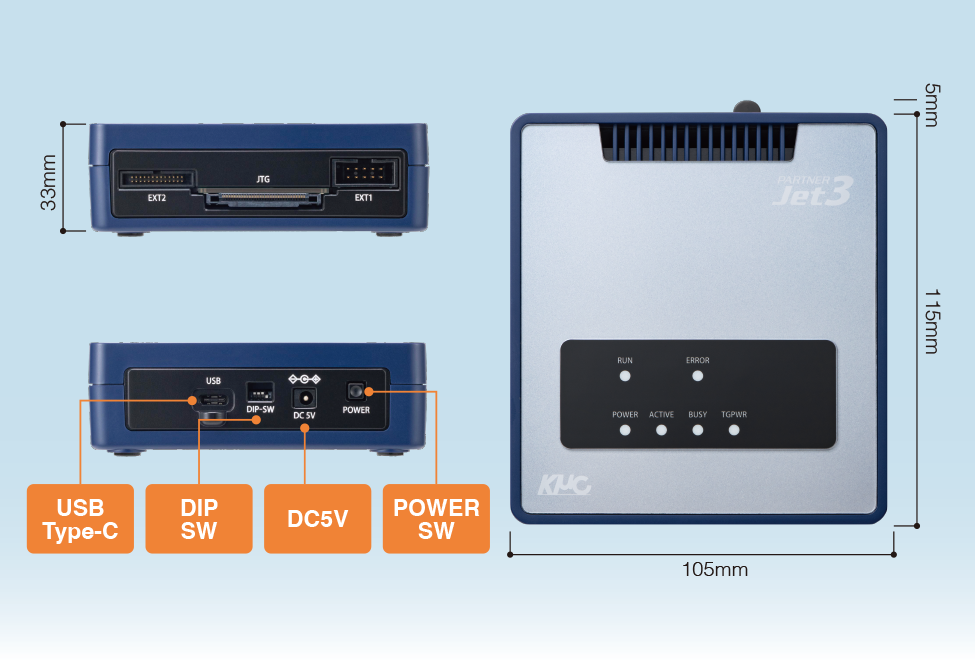

JTAGエミュレータ PARTNER-Jet3

ターゲットボードと接続するJTAGエミュレータボックスです。PARTNER-Jet3は、JTAGデバッグ機能を搭載したModel10をベースとし、トレース機能を強化したModel15をラインナップしています。Model10およびModel15共にUSBバスパワーでの動作が可能です。

JTAGプローブ

PARTNER-Jet3とターゲットボードを接続するためのプローブです。Standard-20pinプローブ(2.54mmピッチ)、Halfpitch-10/20pinプローブ(1.27mmピッチ)、Mictor-38pinプローブの3種類をラインナップしています。Mictor-38pinプローブおよびHalfpitch-10/20pinプローブでは、トレース信号もサポートしています。

また、各種ターゲットボードに接続する変換アダプタも用意しています。

PARTNERデバッガ

ホストPC上で動作するソースコードデバッガです。PARTNERデバッガは、C/C++言語に加え最新のRust言語によるデバッグも可能で、マルチコア構成や32bit命令/64bit命令(Armv8, Armv9, RISC-V)にも対応しています。PARTNERデバッガはCPUコア毎にラインナップしています。

PARTNER Linuxデバッガ

PARTNERデバッガ上で、Linuxアプリケーションをデバッグ有効にするためのオプションライセンスです。

PARTNER-Jet3

PARTNER-Jet3はデバッグテクノロジによる進化ばかりでなく、使い勝手を重視しレスポンスの高速化や利便性を向上させています。プログラム容量が飛躍的に増加している時代だからこそ、PARTNER-Jet3はプログラムダウンロード時のイライラや、ブレーク時のデータアップロード待ちによるストレスを低減するための進化も続けています。

ベースモデルと高機能モデルの2製品をラインナップ

PARTNER-Jet3は、基本プログラムデバッグ機能を備えたModel10をベースとし、トレース機能を強化したModel15をラインナップしています。Model15は、4/8bitの200MHz DDRトレースバスI/Fを備え、512Mバイトのトレースメモリを搭載しています。

PARTNER-Jet3とホストPCとUSB3.2Gen1/2.0で接続します。

Arm®コア/RISC-Vコアに対応

PARTNER-Jet3はArm/RISC-Vに対応し、シングルCPU構成からマルチCPU構成のシステム開発にご利用頂けます。また、Arm社の最新CPUアーキテクチャであるArmv9にも対応し、PARTNER-Jet3で、32bitアーキテクチャに加え、64bitアーキテクチャCPUでのデバッグも可能です。

また、Arm CoreSight™のトレース機能(ETB,ETR,ETM,PTM)にも対応しています。

リアルタイム実行トレース

高速トレース・インタフェース

PARTNER-Jet3 Model15は、リアルタイムにトレースデータを取得することが可能です。高速でデリケートなトレース入力信号をPARTNER-Jet3のキャリブレーション機能でスキュー調整を行うことで、Mictor-38pinプローブまたはHalfpitch-10/20pinプローブを使用することで最大 400Mbps/端子以上(200MHzDDR駆動、4 or 8bit幅)速度でトレースデータを取得することができます。

大容量トレース・メモリ

Model 15では512Mバイトのトレースメモリを備えており、大容量トレースデータを取得することができます。

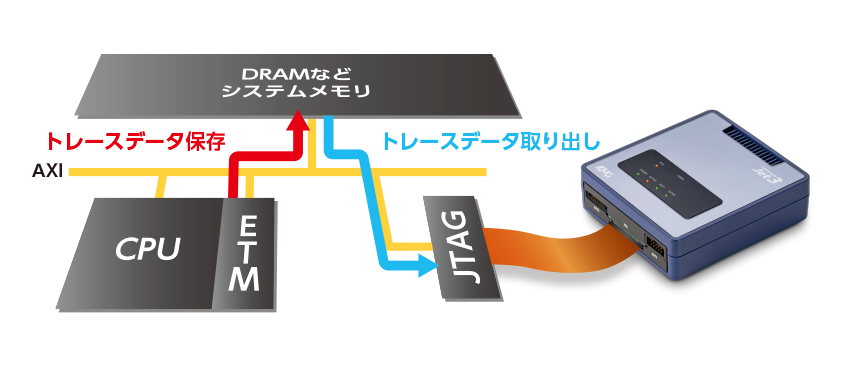

Arm CoreSight ETRトレース対応

Arm CoreSight ETR(組込みトレースルーター)によるトレースデータ取得が可能です。Arm Cortex®プロセッサのETM(組み込みトレースマクロセル)から出力される実行命令トレース情報をターゲット上のシステムメモリにいったん保存し、デバッガはJTAG信号経由でシステムメモリからトレース情報を取得し、ホストPCへ転送します。トレースデータはJTAGポート経由で取得するため、PARTNER-Jet3 Model10でもETRトレースを使用することができます。

USBバスパワー給電

PARTNER-Jet3 Model10およびModel15は、USBバスパワー給電による動作も可能です。ホストPCとのインタフェースは、USB3.2Gen1およびUSB2.0に対応しており、ACアダプタの接続なしでUSB接続するだけで、PARTNER-Jet3を用いたデバッグやプログラム実行トレースを行うことができます。PARTNER-Jet3には供給電力監視機能を搭載しており、電力供給が不足するときはLED点灯でお知らせします。

プローブホットプラグ機能

ターゲットボード動作中に、JTAGプローブやトレースプローブの挿抜が可能です。障害発生時、リセットや電源再投入を介さずに、プローブ接続して直ぐに原因調査&デバッグが出来ます。さらに、スナップショット機能を組合わせれば、常時JTAGエミュレータを接続する必要もなく、不具合発生時の内部状態を丸ごと保存できます。

PARTNER-Jet3機能仕様一覧

| Model10 | Model15 | ||

|---|---|---|---|

| JTAGクロック | 70MHz | ||

| トレースソース | ETB/ITM/ETR (トレース端子不要) | ○ | ○ |

| TPIU (トレース端子使用 4/8bit*1) | ー | ○ (200MHz DDR) | |

| トレースメモリ | PARTNER-Jet3内蔵トレースメモリ | ー | 512Mバイト |

| ホストPC | 接続インタフェース | USB3.2Gen1(推奨)/USB2.0 | |

| OS | Windows 10/11以降 | ||

| 電源仕様 | USBバスパワー | ○ | ○ |

| ターゲット信号電圧(JTAG信号およびトレース信号) | 1.6V~3.6V | 1.6V~3.6V | |

| ACアダプタ | IN: AC100-240V OUT: DC5V | ||

| 本体外形サイズ(突起部を除く) | 105*115*33 mm | ||

| 動作温度 | 5~35℃ 湿度85%以下(結露なきこと) | ||

PARTNERデバッガ(1)

開発エンジニアの皆様と共に進化を極め、ソースコードデバッグを行うときに必要な機能を豊富に備えたデバッガです。ハードウエアの立ち上げ段階からソフトウェアの性能評価まで、開発の全てのステージでエンジニアを支援します。

ソースコードデバッガ

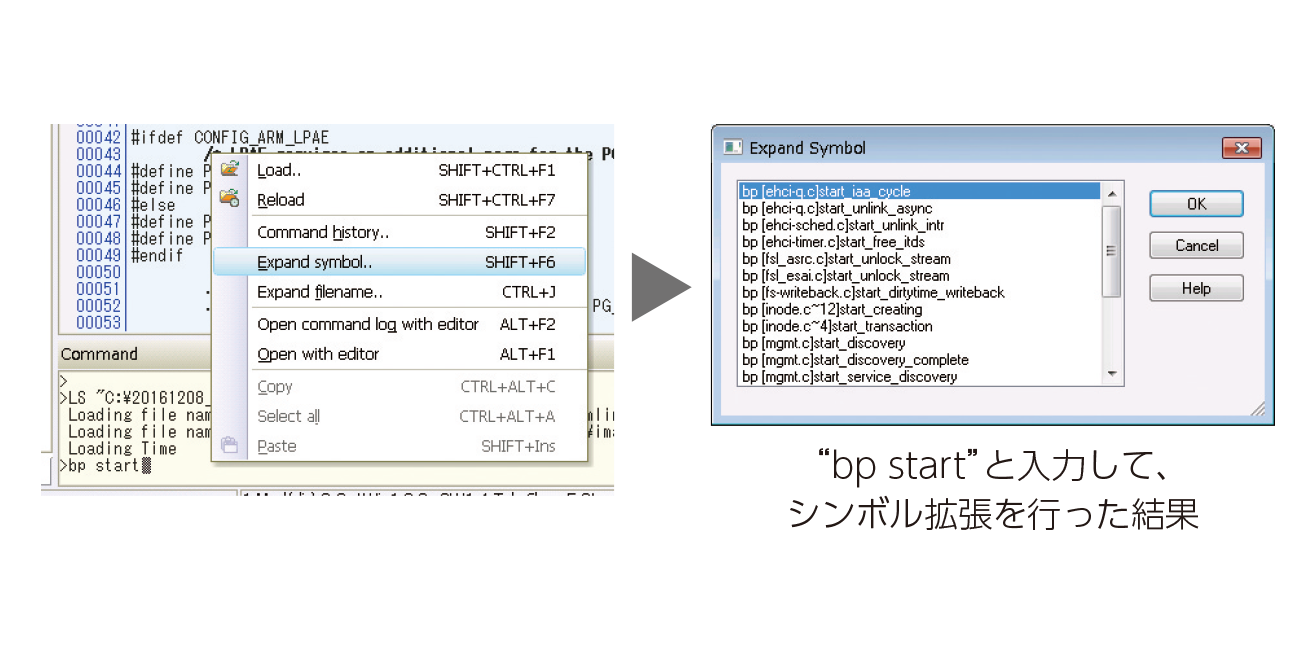

ビルド・ロードしたプログラムは、ソースコード上で実行指定やプログラムカウンタの移動、ソースコード行のクリックでブレークポイント設定などの操作が可能です。またソースコード上の変数をクリックするだけで変数の値をインスペクト表示します(C/C++/Rust 言語に対応)。 さらにコーディングやデバッグに便利な以下の機能も備えています。

- 実行プログラムをロードした後で、シンボル情報などのデバッグ情報だけを追加で読み込むことができます(複数読み込み可)。

- シンボル名の入力途中で候補を表示し選択できる、入力補完機能があります(シンボル拡張、下図)。

- プリプロセッサマクロ展開結果をデバッガ表示(対応コンパイラのみ)。

- 各ウィンドウやコマンドの結果を、指定した外部エディタで表示・テキスト保存できます。

- 連続ステップ実行した履歴をたどることができます。

- 関数呼び出し履歴表示および、履歴に表示された関数内でのローカル変数の値を連動表示します.。

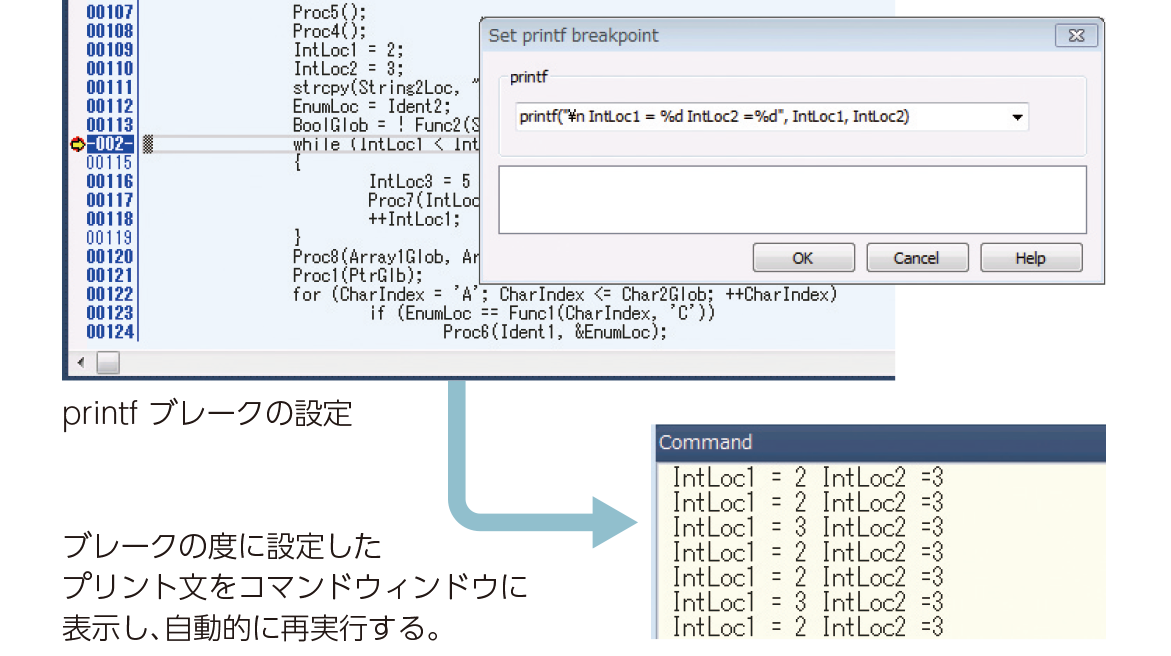

ブレークポイント

デバッガの基本機能であるブレーク機能として、ソフトウェアブレークとハードウェアブレークがあります。S/W ブレークは指定した箇所の命令をブレーク専用の命令に置き換えて、プログラムの実行を停止させます。PARTNER デバッガでは、 ソフトウェアブレークが発生したときにマクロの実行、コマンド実行や printf のようなメッセージをデバッガのウィンドウに出力する機能があります。ソフトウェアブレークは最大63点まで指定できます。 ハードウェアブレークは、デバッグ対象のプロセッサーのオンチップデバッグ機能を使ってプログラムを停止させる機能です。アドレス条件、データ条件やリード・ライト条件などを指定(CPUにより条件が異なる)することで、特定のメモリへの不正ライトによるメモリ破壊などの検出に役立ちます。

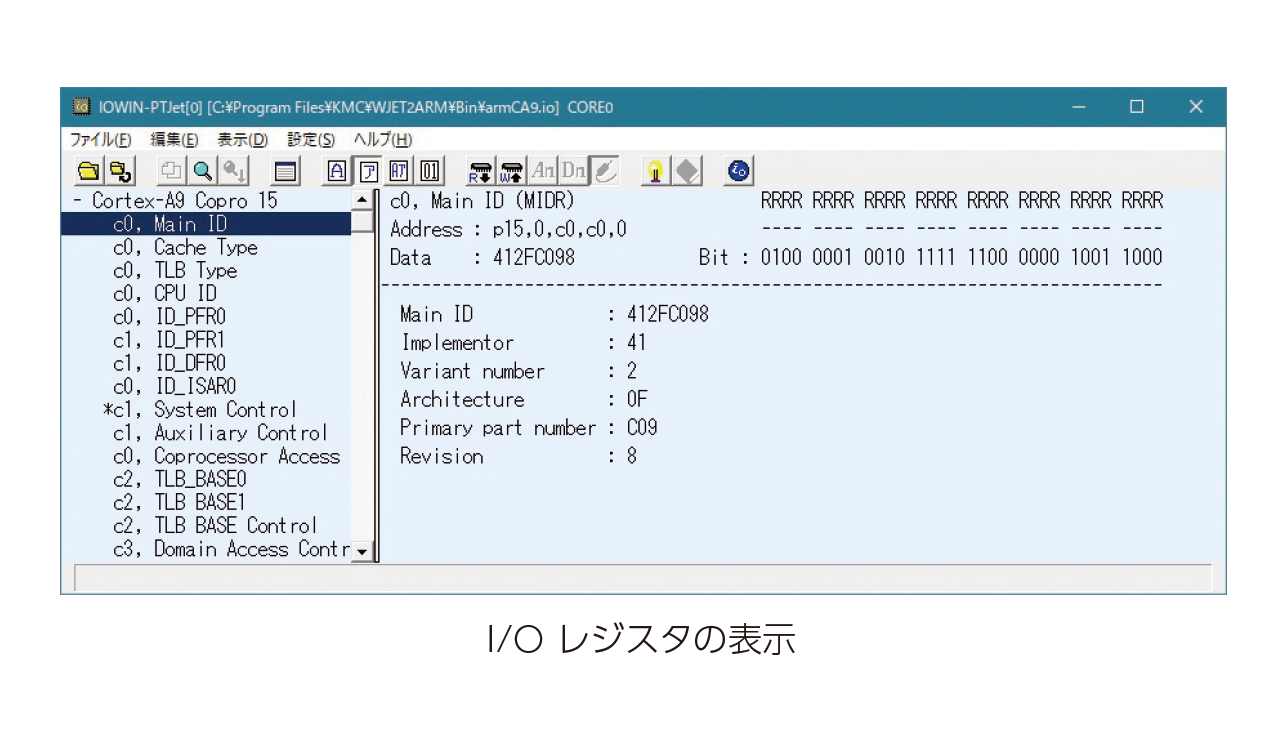

I/Oレジスタ機能

周辺系I/Oのレジスタを定義したファイルをロードすることにより、レジスタの名前やビットアサイン、ビットの意味などを分かりやすいGUIで表示したり、ビットフィールド単位で値の変更が可能です。定義ファイルはテキストエディタ等で作成できます。

PARTNER-Jet3独自のIO定義ファイル以外にArm® CMSIS-SVD ファイルにも対応しています。

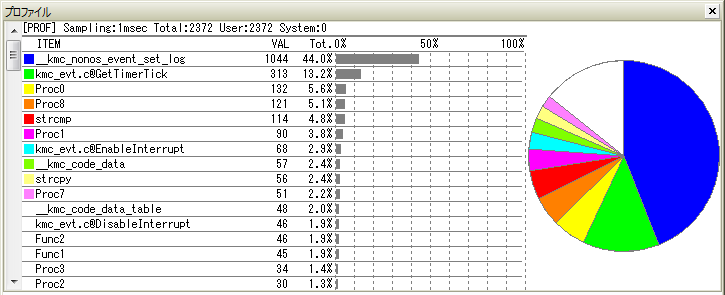

プロファイリング

一定周期でPC(プログラムカウンタ)をモニタリグし、プログラムの実行プロファイルを取得することができます。関数の読出し頻度や実行時間を知ることで、ボトルネックとなっている関数を見つけることができ、システムチューニングに役立ちます。

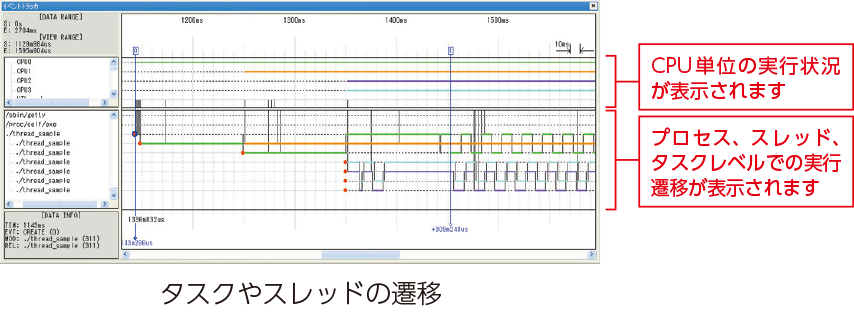

イベントトラッカ―

タスクやスレッドの遷移をGUIで表示し、OSを使ったソフトウェアの動作解析を容易にします。イベント情報はターゲットメモリ内に保存する他、Model 15ではリアルタイムトレースとの連携や、埋め込みトレースとの連携も可能です。

NORTi, T-Kernel, Toppers, uC3のOSに対応しています。ソースコードが添付されていますので、簡単に他OSにも対応させることが可能です。

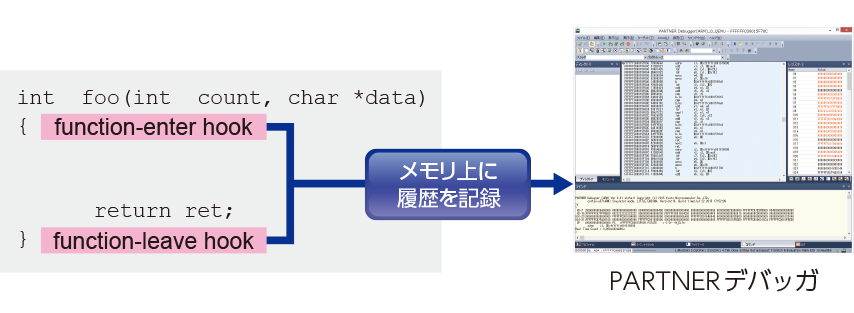

埋め込みトレース(Model15)

トレース信号を持たないターゲットハードウェアに対して、ターゲット上のメモリを使いJTAG接続だけで関数レベルの実行履歴を取得する機能です。 関数の入口/出口にトレースフックルーチンを埋め込み、そのフックルーチン通過の際に出力されるデータをターゲットシステム上のメモリに記録し、デバッガ上で履歴表示します。 必要な箇所にトレースポイントを埋め込めば、トレースデータの生成量を抑制し、少ないメモリ容量で長時間のトレースデータを取得することができます。

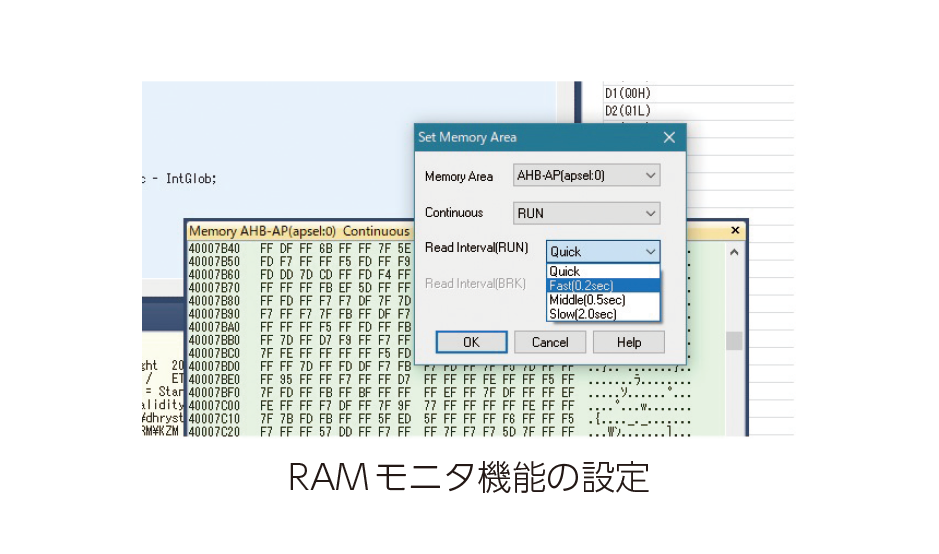

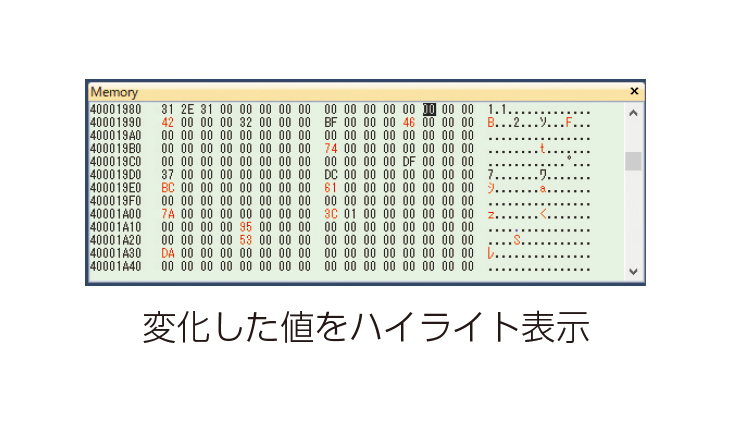

RAMモニタ機能

Arm CoreSight™ AXI-AP(AHB-AP)を使用したCPUを介さないメモリアクセスにより、実行中のRAMの内容をメモリウィンドウにリアルタイムに表示することができます。

こんな時に、RAMモニタは効果を発揮します。

- 停止できないメカ制御でのパラメータ領域の監視ができます

- PARTNER-Jet3のプローブホットプラグ機能と組み合わせることで、長時間稼働中のシステムをリセットやブレークさせることなくデバッガを接続して、データを監視することが可能です。

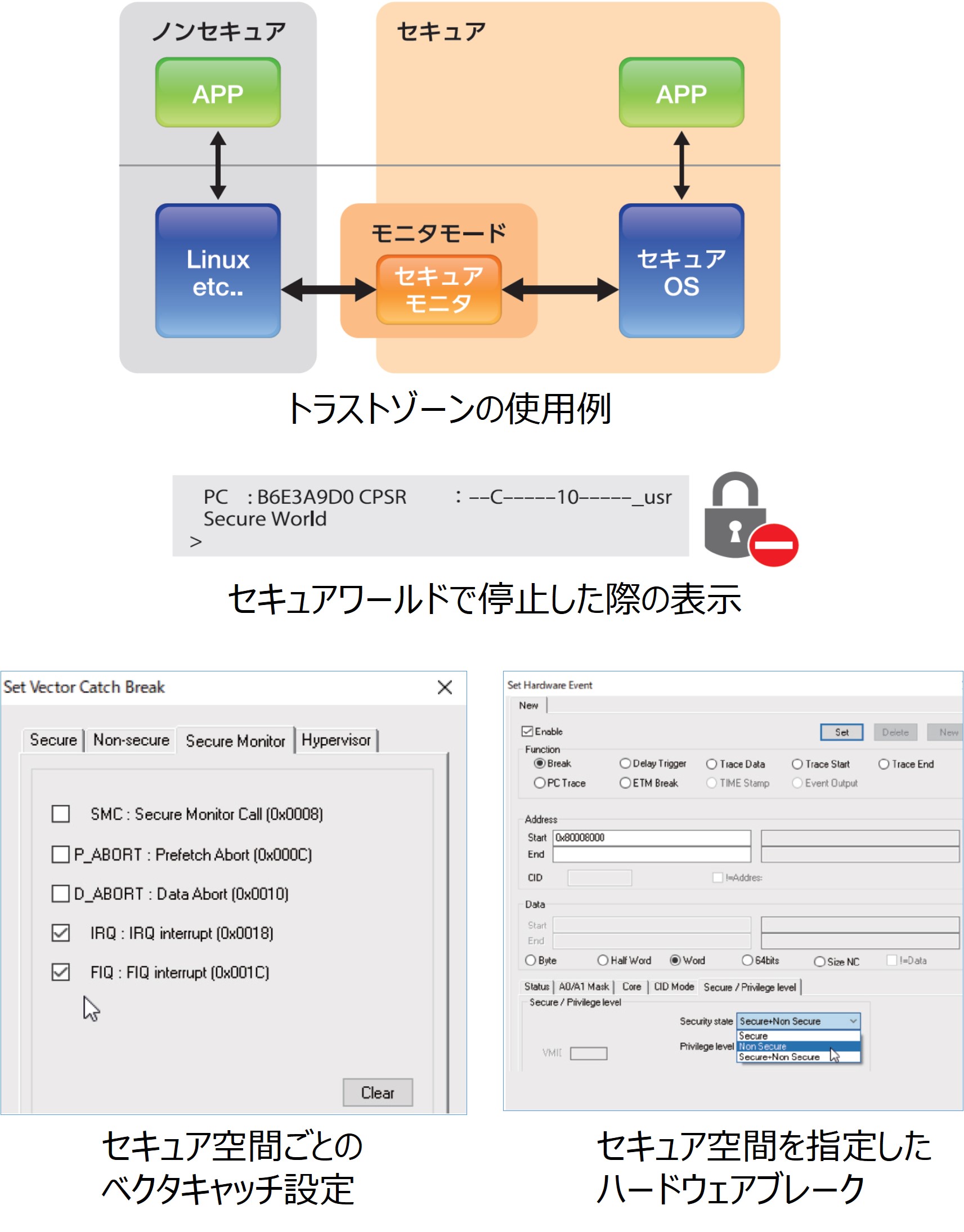

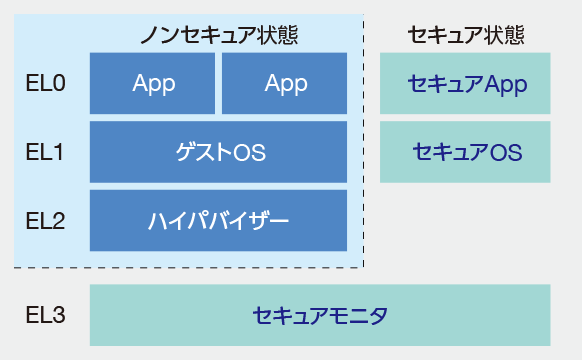

TrustZone®のデバッグ対応

トラストゾーンは、主にArm Cortex®-Aのプロセッサ向けの拡張機能で、アクセス保護が必要なデータやソフトウェアが動作する「セキュアワールド」と、それ以外の「ノンセキュアワールド」にメモリ空間を分離することができます。ノンセキュアワールドとセキュアワールド間の切り替えは、モニターモード(mon)で動作するセキュアモニタを通して行われます。

PARTNERでは、これらの状態を、ステータスバーや実行停止時のコマンドウィンドウの表示から知ることができます。また、ハードウェアブレークやベクタキャッチのオプションで、有効となる状態を指定すれば、ノンセキュアワールドでのみ停止するようなブレークポイントや、セキュアモニタに切り替わった直後に停止するベクタキャッチなどの作成が可能です。ただし、ハードウェアでセキュアワールドのデバッグが禁止されている場合は、セキュアワールドやセキュアモニタの実行中に停止させることはできません。セキュアワールドでのプログラム実行中にブレーク要求が発生した場合はそのブレーク要求が保留され、セキュアワールドからノンセキュアワールドに分岐した瞬間にブレークします。

Armv8-A, Arm v9-Aアーキテクチャ対応

Arm-v8/Arm-v9 64bit アーキテクチャ(AArch64)向けに、新たに定義された4階層のException Level (EL0 ~ EL3)とセキュア/ノンセキュア状態での動作がデバッグしやすいよう、PARTNERデバッガ機能を拡張しています。

- H/Wブレーク条件に、Exception Levelとセキュア状態を設定可能

- H/Wブレーク条件に、仮想マシンIDを指定可能

- 指定したException Levelへの遷移をブレーク条件に指定できる、Exceptionキャッチブレークを新設

- ステータスバーにException Levelとセキュア状態を表示

- ETM/PTMトレースにException Levelとセキュア状態を表示

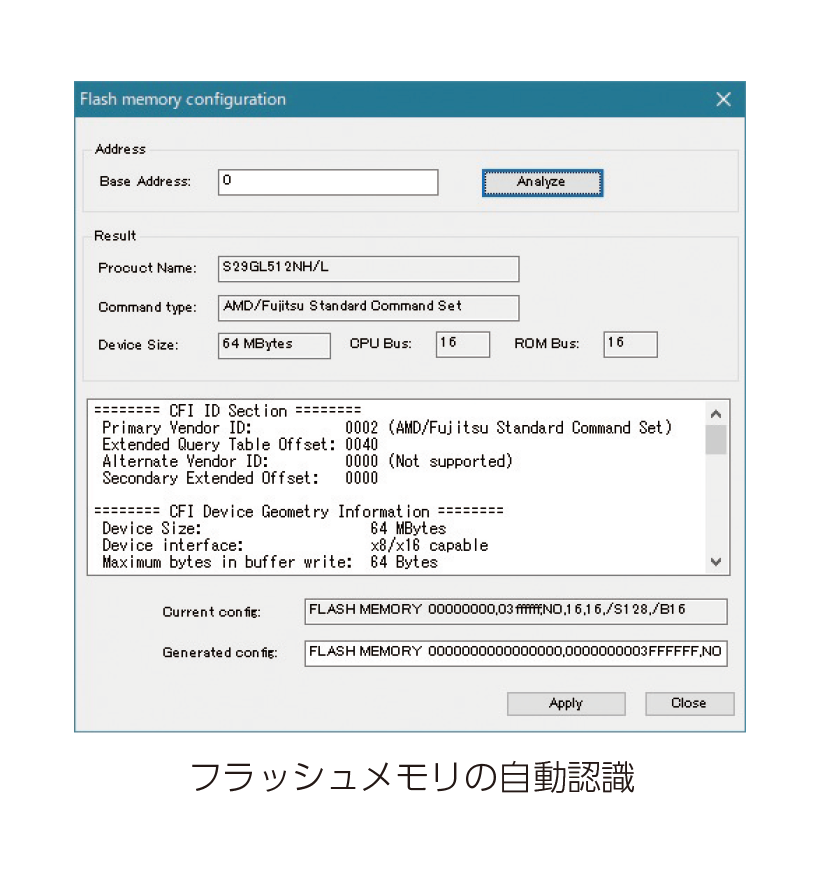

フラッシュメモリ対応

各種NORフラッシュメモリの書き込みに対応しており、NORフラッシュ上をXIP実行するプログラムに対してブレークポイントを設定することも可能です。 SPI接続したNORフラッシュメモリは、当社が提供するSDKで書き込み用のモニタプログラムを作成することにより、標準サポートのパラレル接続のNORフラッシュと同様に書き込みができます。HyperFlash™の場合もパラレルNORフラッシュと同等の書き込み機能を利用することができます。 パラレルNORフラッシュとHyperFlash™ではCFIからフラッシュメモリ情報を取得することで、フラッシュ書き込み設定を自動で行います。

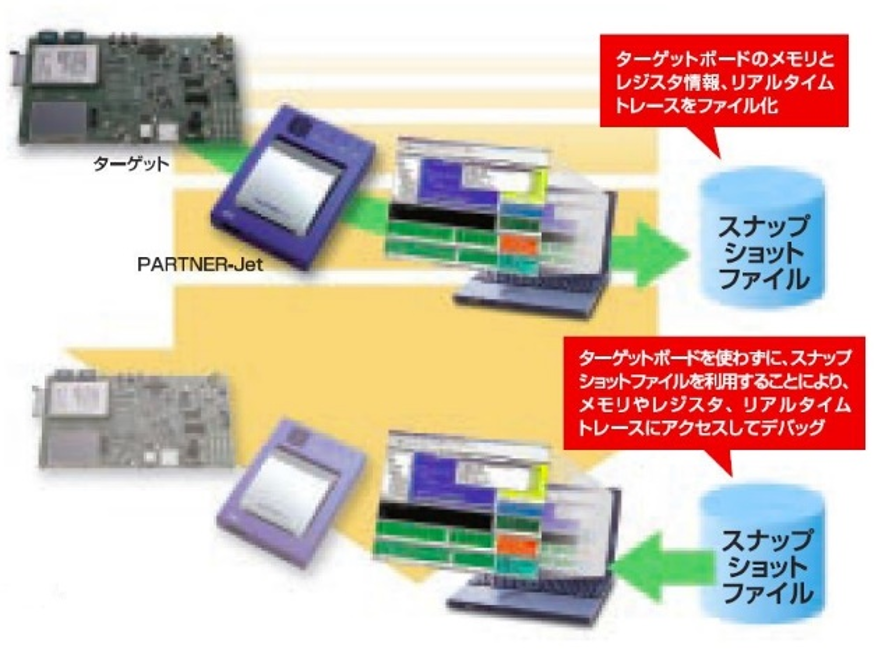

スナップショット

コマンド入力で、CPUの状態、物理メモリの内容、リアルタイムトレースデータをファイルに保存します。後で、保存データを、PARTNERデバッガに読み込めば、ターゲットボードを接続せずとも、データ取得時の状態を復元することができます。 例えば、不具合時に取得したスナップショット・データを開発メンバ間で共有し、手分けして原因究明を行う場合などに有用です。

スクリプト機能

デバッグ時の作業をプログラマブルに実行するためのスクリプト機能を搭載しています。PARTNERデバッガのスクリプト言語は、C言語に似た構文で使いやすいSquirrel言語の他に、多く使われているPythonにも対応しており、利用目的や、好み・慣れで使い分ける事ができるようになっています。 また、Pythonスクリプトは、起動ステート(リセット前・中・後、CoreSight DAP初期化前・後)でも実行させることが可能です。起動ステートでスクリプトを実行させることで、JTAG接続確立前に、ターゲットLSIとの認証を行うなど、JTAGアクセスのセキュリティ確保にも役立ちます。

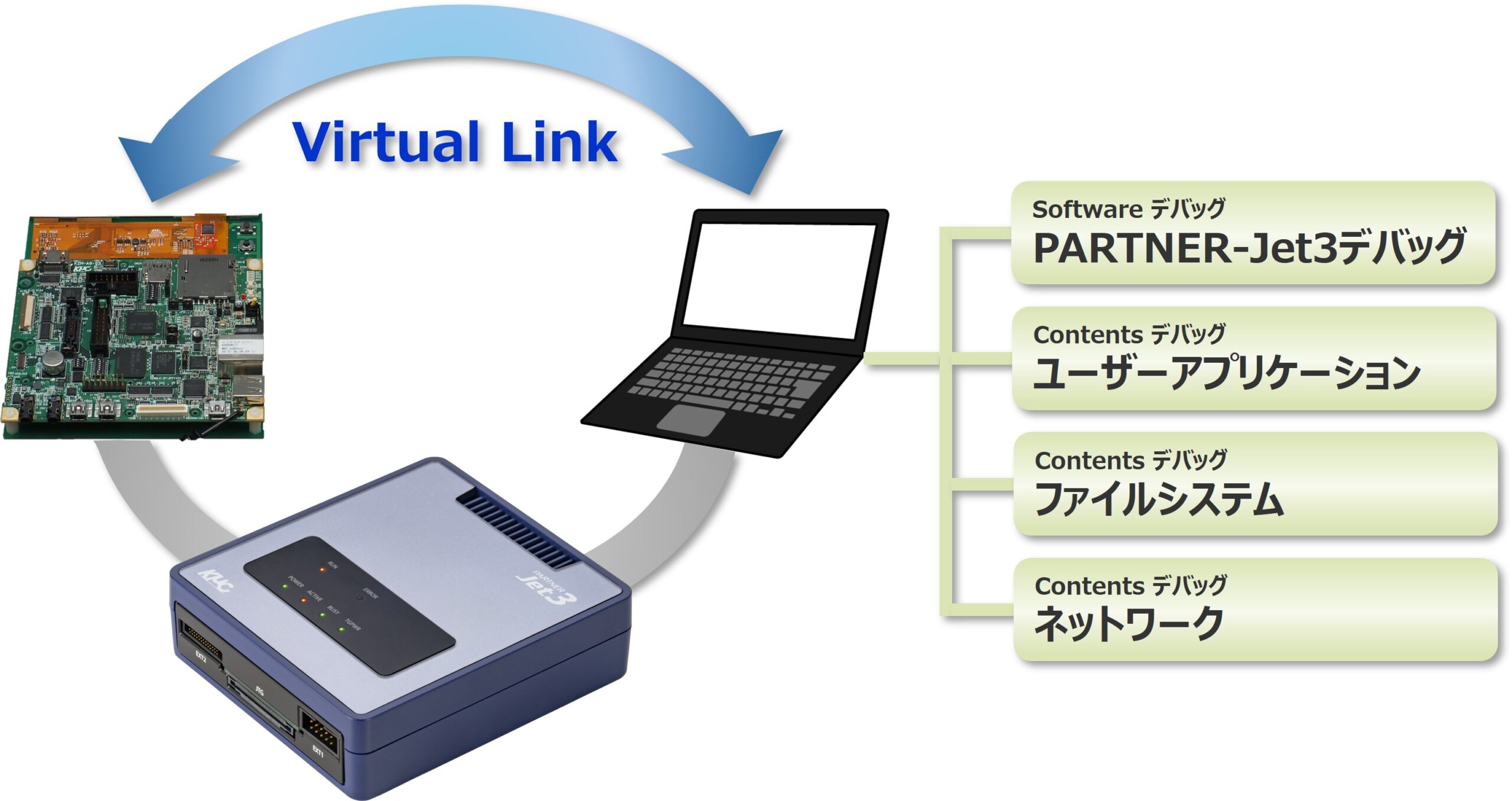

VLINK機能

GCCコンパイラと連携し、VLINKサポートライブラリを含むターゲットコードを生成することで、ターゲットプログラムからホストPC上のファイルシステムなどに(PC上のプログラムと同様に)アクセス可能です。

PARTNERデバッガ(2)

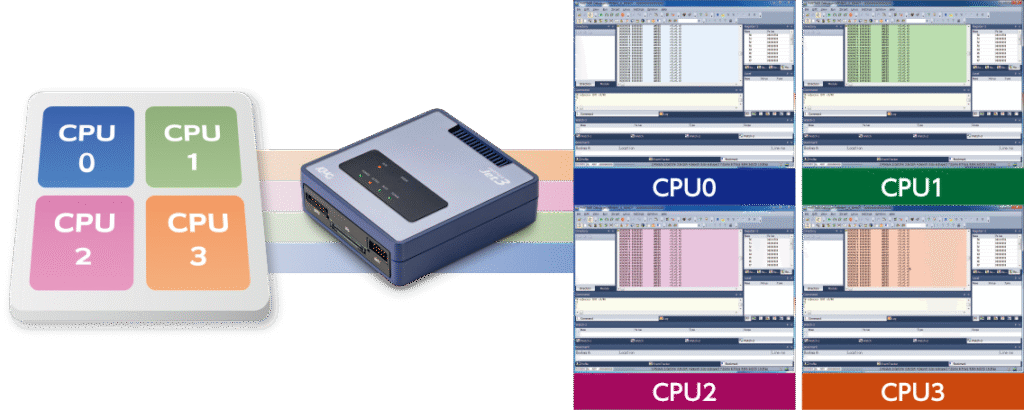

PARTNERデバッガは、マルチコアデバッグ時でも、高速排他制御と仮想化技術によりシングルコアデバッグのように、高速でストレスのないデバッグ環境を提供しています。

様々なマルチコア構成に対応

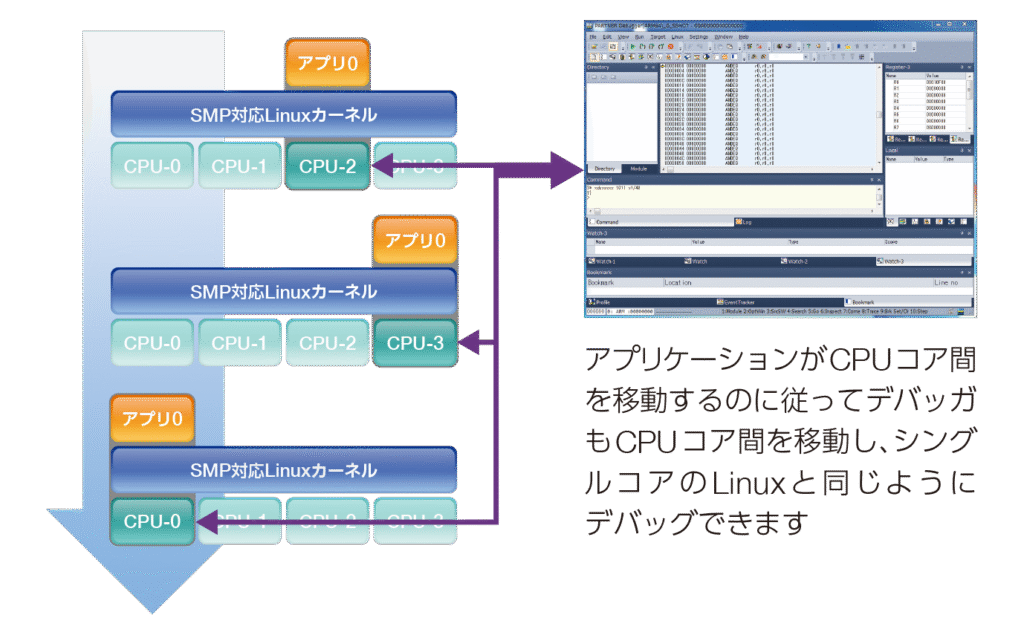

SMPデバッグ

SMP Linuxなど、OSが複数のプロセッサーをコントロールする場合には、1つのデバッガウィンドウで、対象の複数プロセッサーをまとめてデバッグできます。SMP OS上で動作するプログラムがプロセッサー間を移動しても、ユーザは、それを意識せずにデバッグすることができます。

AMPデバッグ

CPU毎に異なるOSを実行するシステムや、CPU毎に独立した処理を割り当て実行するシステムでは、プロセッサ毎にデバッガウィンドウを起動して、個々のプログラム・デバッグが可能です。1台のJTAGエミュレータで複数CPUを同時にデバッグすることができます。

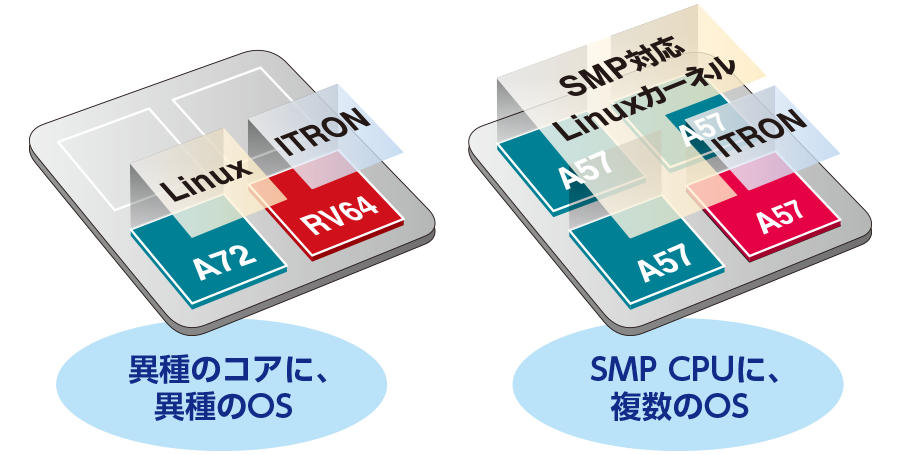

こんな構成でもデバッグが可能です。

・Cortex®-A53とCortex-R5のように、コア種が異なりかつAArch64/AArch32のように異なるアーキテクチャの構成

・LinuxとITRONのように異なるOSの構成

・異なるコンパイラで作成されたプログラムを、個々のCPUで実行する構成

・SMPグループとAMPのプロセッサーとの組み合わた構成

例:Cortex-A53 QuadコアのSMP Linuxと、Cortex-R5のリアルタイムOS

異なるコア/異なるOSに対応

AMP構成のシステムにおいては、Cortex-A53とCortex-R5のように、 CPU毎のトレース情報を利用し、関数やコンテキスト単位でソフトウェアのふるまいを可視化。種類が異なりかつAArch64/AArch32のようにアーキテクチャも異なる複数のプロセッサーを同時にデバッグできます。また、LinuxとITRONのように異なるOSや、異なるコンパイラで作成されたプログラムも同時にデバッグできます。 さらに、Cortex-A53 QuadコアのSMP Linuxと、Cortex-R5のリアルタイムOSの様に、SMPグループとAMPのプロセッサーとの組み合わせも、同期・非同期でのデバッグができます。

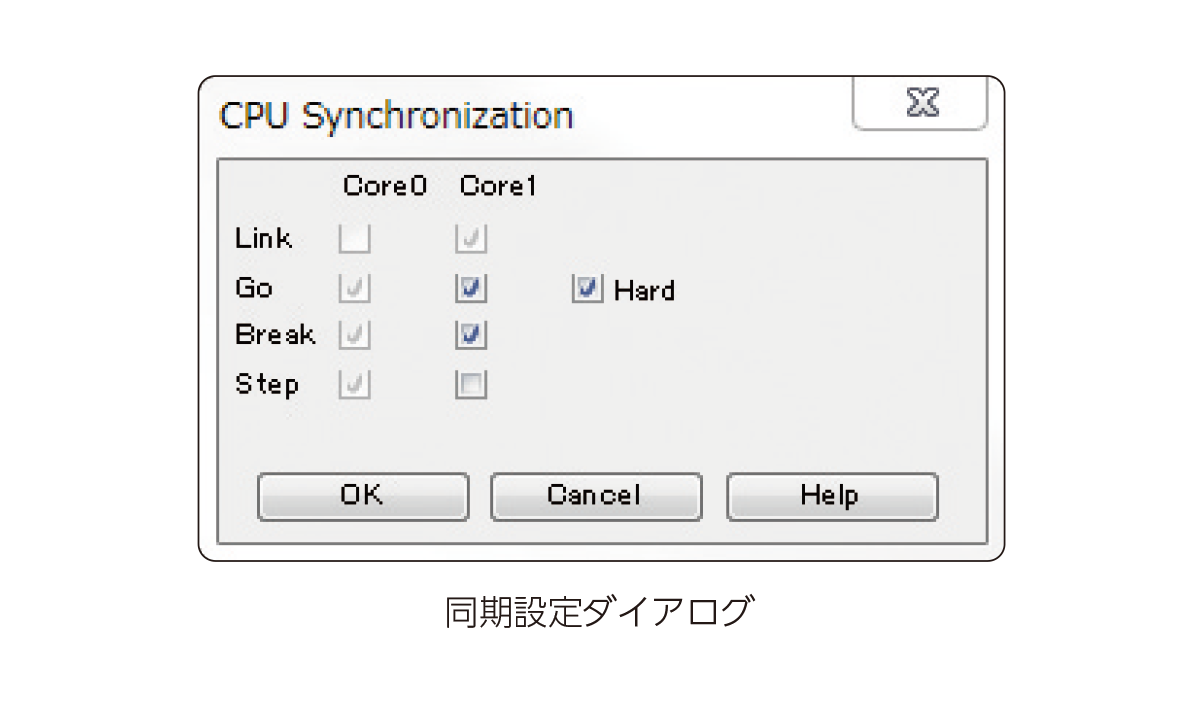

マルチコアでのデバッグ

CPUコア間の同期デバッグ

AMP構成の場合、各CPUコアを完全に独立して動作させる、もしくはgo/breakを同期させた状態でのデバッグが選択できます。(SMP設定のCPUコアでは、常に同期設定で動作します)

PARTNER デバッガはCoreSight™ CTI などのコア間同期機能に対応しており、クロックレベルでの同期実行・ブレークが可能です。

デバッグ対象のハードウェアに同期機能が無い場合は、ソフトウェアでの同期が可能です。

マルチCPUコア構成でのブレークポイント制御

ソフトウェアブレークポイントは、各CPUコアの設定数の合計が最大63点まで使用できます。複数のデバッガから、同じ物理アドレスにソフトウェアブレークポイントを設定した場合には、CPUコア間でのブレークポイントの競合をPARTNER-Jet3が自動的に解決します。また、1 つのCPUコア(デバッガ)に対して指定したソフトウェアブレークポイントと同じアドレスの命令を、他のCPUコアが実行した場合にはデバッガを停止させないといった排他処理も、PARTNERデバッガが高速に制御しています。

ハードウェアブレークポイントはCPUコアごとにブレーク条件を設定できるだけでなく、SMP構成の場合には、複数のCPUコアに同時に同じ条件でブレークポイントの設定が可能です。

リアルタイムトレースの同時取得

Cortex-A53とCortex-R7のように異なる種類のCPUコアのマルチシステムの場合、同時にトレース情報を取得し、時間同期したトレースデータを取得することが可能です。 しかし、同時に複数のCPUコアのトレース情報を取得すると、トレース情報が増えるため転送されるトレースパケットがオーバーフローする可能性があります。このような場合には、トレースデータを取得するプロセッサを指定することで、トレースパケットのオーバーフローの抑制することが可能です。

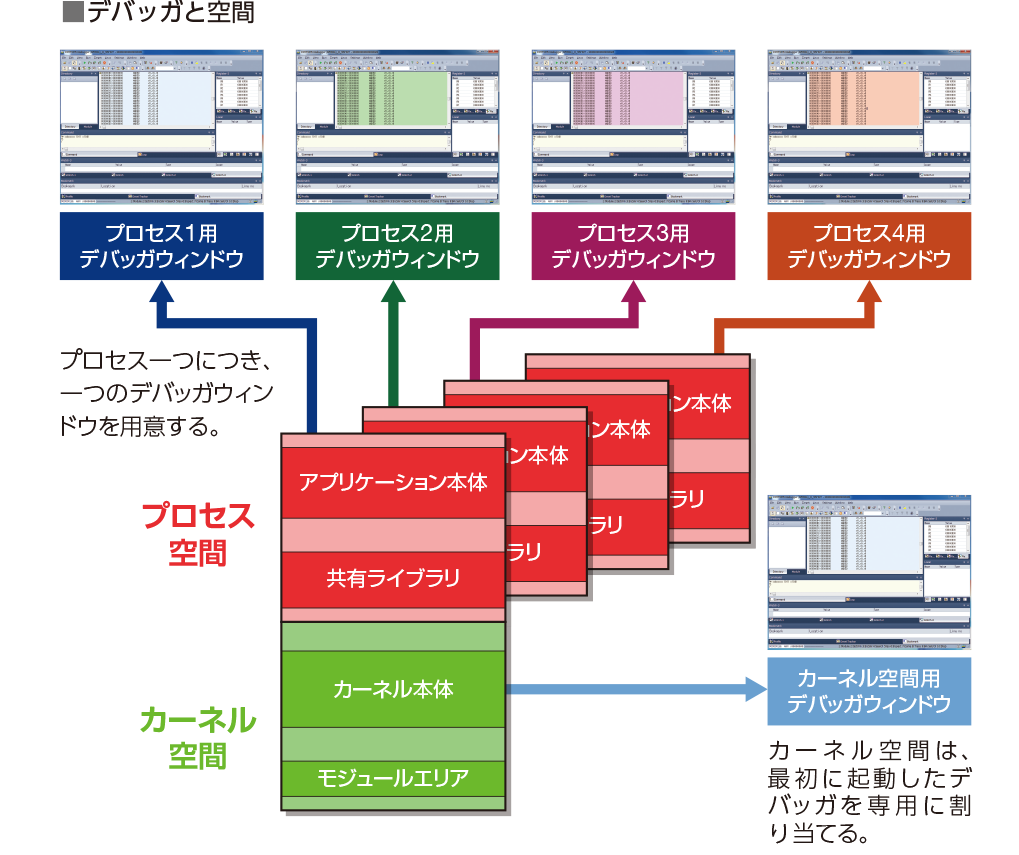

Linuxデバッガ

Linuxデバッガは、PARTNERデバッガ上でLinuxプログラムをデバッグするための製品です。Linuxデバッガを組み込むことで、ローダブルモジュール、アプリケーション、共有ライブラリのデバッグが可能となり、ブートローダ/カーネルを含む全てのプログラムのデバッグできます。

Linuxデバッグ対象

64bit Linux、LPAE Linux、thumb2ビルドカーネルに対応するとともに、“デバッグパッチを適用したカーネル”、“デバッグパッチ無しのカーネル”のいずれにおいても、アプリケーション/ローダブル・モジュールのデバッグが可能です。

デバッガから見たLinuxのプログラムの種別と特徴

| プログラム種別 | 空間 | アドレス | ページング | デバッグ |

|---|---|---|---|---|

| ブートローダ | 非MMU空間 | 固定番地 | なし | 既存の組込みデバッグに同じ |

| カーネル | MMU上の単一カーネル空間 | 固定番地 | (ほぼ)なし | 既存の組込みデバッグに(ほぼ)同じ |

| ローダブルモジュール | MMCU上の単一カーネル空間 | リロケータブル | デマンドページング | リロケーション解決、ページングへの対応が必要 |

| アプリケーション | MMU上の論理多重仮想空間 | 固定番地 | デマンドページング | 論理多重空間、ページングへの対応が必要 |

| 共有ライブラリ | MMU上の論理多重仮想空間 | リロケータブル | デマンドページング | リロケーション解決、論理多重空間、ページングへの対応が必要 |

ブートローダ

ブートローダでは、実行を開始してから、オブジェクトコードを外部メモリ等にコピーし、そこに制御を移動して動作するタイプのものもあります。このようなタイプのブートローダに対応するため、PARTNERデバッガでは、ブートローダのシンボル情報を読み込む際にアドレスオフセットを指定し、1つのオブジェクトを移動前と移動後の両方のアドレスに対応させることで、ソースデバッグを可能にしています。

カーネル

カーネル空間は単一の固定アドレスで動作するため、通常は特別な設定をしなくてもデバッグが可能です。カーネルがSMP構成の場合には、複数のプロセッサーに対して個別にデバッガを接続し同時にその状態を見ることができるため、カーネルのブート時のデバッグが容易に行えます。 またLinux 4.x 以降のカーネルでは、“idle 時にコアの電源を落とす”、“デバッグ中に一定時間ブレーク状態が続くと、警告のメッセージをコンソールに出力する”というように、デバッグをしづらくする機能が多数追加されています。このような問題に対処するため、カーネルのコンフィグレーションの変更やコマンドラインの追加で問題を回避・抑制する方法を具体的にマニュアルでガイドしています。

ローダブルモジュール

Linuxのローダブル・モジュールは、アドレス情報を持たないリロケータブルなオブジェクトで、insmodコマンドが実行された 時にアドレスが確定します。PARTNERデバッガは、insmodコマンドが実行された時にカーネル内のモジュールのメモリマップを調べてシンボル情報を読み込むことで、ローダブル・モジュールのソースデバッグを実現しています。 ユーザは、デバッグしたいローダブル・モジュールを登録してinsmodコマンドを実行するだけで、モジュールの先頭からデバッグできます。

アプリケーション

Linuxのアプリケーションは多重仮想空間になっており、全てのアプリケーションは、同じアドレス範囲で動作します。そのため、単一の空間で動作するプログラムのようにアドレス情報だけでアプリケーションを識別できません。PARTNER デバッガは、Linuxアプリケーション個別の空間を認識することでアプリケーションのデバッグを実現していています。複数のアプリケーションをデバッグする際は、デバッガウィンドウを複数起動し、それぞれのアプリの専用デバッガとして対象のアプリのシンボルをロードしてソースコードデバッグができます。main()からのデバッグ、実行中のプロセスのデバッグにも対応できます。 またマルチプロセス、マルチスレッドのデバッグにも対応しています。

共有ライブラリ

デバッグ中のアプリケーションにリンクされている共有ライブラリをデバッグする場合は、リンクされている共有ライブラリ名やマップ情報をPARTNERデバッガが自動認識してシンボル情報を読み込むので、ソースコードデバッグが可能です。

SMP Linuxのデバッグ

SMPマルチコア向けLinuxでは、アプリケーションが実行権を得るたびに、アプリケーションを実行するCPUコアが変わります。実行するCPUコアの移動に従ってデバッガもCPUコア間を移動します。エンジニアは、STM Linuxを意識せず、シングルコアのLinux と同じようにデバッグできます。

デバッグ情報キャッシュ機能

組込みLinuxの64bit対応により、vmlinuxのシンボル情報が非常に大きくなり、シンボル情報の解析に時間がかかるようになりました。PARTNERデバッガは解析時間によるストレスを軽減するため、カーネルのシンボル情報をホストPCにキャッシュする機能を実装しています。10秒以上かかっていたシンボル情報解析が1秒以下になりました。 ※デバッグ情報キャッシュ機能はLinux カーネル専用ではありません。

teraterm連携機能

teraterm連携機能は、u-bootやLinuxのコンソール(teraterm)入出力を、PARTNER デバッガのコマンドウィンドウ経由で入出力する機能です。デバッグ開始時にPARTNERデバッガのマクロで、カーネルシンボルロードや、ブレークポイント設定を自動化することに加えて、 teraterm連携機能を使うことにより、 Linuxへのログインやアプリケーション実行までも、Linuxのコンソールを操作することなくマクロを使った自動化が可能です。 ※ホストPCにteratermがインストールされている必要があります。

Linuxデバッグ機能別対応リスト

|

デバッグ対象 | カーネル |

| ローダブル・モジュール | |

| アプリケーション | |

| 特別なアプリ(init=プロセスID1番) | |

| マルチプロセス | |

| マルチスレッド | |

| デバッグ機能(カーネル空間) | ソフトウェアブレーク |

| ハードウェアブレーク(命令実行) | |

| ハードウェアブレーク(データアクセス) | |

| ソースレベルデバッグ | |

| ローダブル・モジュールの自動リロケーション | |

| デマンドページングの解決 | |

| カーネルブレーク中のプロセスデバッグ | |

| デバッグ機能 (ユーザ空間) | ソフトウェアブレーク |

| ハードウェアブレーク(命令実行) | |

| ハードウェアブレーク(データアクセス) | |

| 実行トレース(分岐トレース) | |

| ソースレベルデバッグ | |

| デマンドページングの解決 | |

| 共有ライブラリの自動リロケーション | |

| 実行中プロセスへのアタッチ | |

| プロセスブレーク中のカーネルデバッグ | |

| プロセスブレーク中のカーネルや他のプロセスの実行* |